CI was not building the a.rs application due to the requirement of b.bin

having been built first. Add a feature flag to examples so that CI can

build them including a dummy application.

Update a.rs application examples so that they compile again.

- Move typelevel interrupts to a special-purpose mod: `embassy_xx::interrupt::typelevel`.

- Reexport the PAC interrupt enum in `embassy_xx::interrupt`.

This has a few advantages:

- The `embassy_xx::interrupt` module is now more "standard".

- It works with `cortex-m` functions for manipulating interrupts, for example.

- It works with RTIC.

- the interrupt enum allows holding value that can be "any interrupt at runtime", this can't be done with typelevel irqs.

- When "const-generics on enums" is stable, we can remove the typelevel interrupts without disruptive changes to `embassy_xx::interrupt`.

1471: embassy-net: Make TcpSocket::abort() async r=Dirbaio a=mkj

This lets callers ensure that the reset packet is sent to the remote host. Otherwise there isn't a way to wait for the smoltcp stack to send the reset.

Requires changes to smoltcp to wake after the reset has been sent, see https://github.com/smoltcp-rs/smoltcp/compare/master...mkj:smoltcp:abort-wake

This commit also adds a "TCP accept" demo of the problem. Without the `.await` for abort() it gets dropped before the RST packet is emitted.

Co-authored-by: Matt Johnston <matt@ucc.asn.au>

1340: Add I2S for f4 r=Dirbaio a=xoviat

This is only for f4, but it puts us equal to or ahead of the standard rust hal.

1474: stm32: Fix watchdog timeout computation r=Dirbaio a=rmja

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

Co-authored-by: Rasmus Melchior Jacobsen <rmja@laesoe.org>

1457: TL Mbox read and write for stm32wb r=xoviat a=OueslatiGhaith

Hello,

This pull request is related to #1397 and #1401, inspired by #24, built upon the work done in #1405 and #1424, and was tested on an stm32wb55rg.

This pull request aims to add read and write functionality to the TL mailbox for stm32wb microcontrollers

Co-authored-by: goueslati <ghaith.oueslati@habemus.com>

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

exposing pac items kind of undermines the unstable-pac feature. directly

exposing register structure is also pretty inconvenient since the clock

switching code takes care of the src/aux difference in behavior, so a

user needn't really be forced to write down decomposed register values.

1458: rp: remove take!, add bind_interrupts! r=Dirbaio a=pennae

both of the uart interrupts now check a flag that only the dma rx path ever sets (and now unsets again on drop) to return early if it's not as they expect. this is ... not our preferred solution, but if bind_interrupts *must* allow mutiple handlers to be specified then this is the only way we can think of that doesn't break uarts.

Co-authored-by: pennae <github@quasiparticle.net>

It was intended to allow changing baudrate on shared spi/i2c. There's no

advantage in using it for PWM or PIO, and makes it less usable because you have to

have `embassy-embedded-hal` as a dep to use it.

1424: add TL maibox for stm32wb r=xoviat a=OueslatiGhaith

Hello,

This pull request is related to #1397 and #1401, inspired by #24, build upon the work done in #1405, and was tested on an stm32wb55rg.

This pull request aims to add the transport layer mailbox for stm32wb microcontrollers. For now it's only capable of initializing it and getting the firmware information

Co-authored-by: goueslati <ghaith.oueslati@habemus.com>

Co-authored-by: Ghaith Oueslati <73850124+OueslatiGhaith@users.noreply.github.com>

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

execution wraps around after the end of instruction memory and wrapping

works with this, so we may as well allow program loading across this

boundary. could be useful for reusing chunks of instruction memory.

the many individual sets aren't very efficient, and almost no checks

were done to ensure that the configuration written to the hardware was

actually valid. this adresses both of these.

programs contain information we could pull from them directly and use to

validate other configuration of the state machine instead of asking the

user to pull them out and hand them to us bit by bit. unfortunately

programs do not specify how many in or out bits they use, so we can only

handle side-set and wrapping jumps like this. it's still something though.

it's only any good for PioPin because there it follows a pattern of gpio

pin alternate functions being named like that, everything else can just

as well be referred to as `pio::Thing`

1429: rp pio, √9 r=Dirbaio a=pennae

another mix of refactoring and soundness issues. most notably pio pins are now checked for being actually accessible to the pio blocks, are constructible from not just the owned peripherals but refs as well, and have their registrations to the pio block reverted once all state machines and the common block has been dropped.

state machines are now also stopped when dropped, and concurrent rx+tx using dma can finally be done in a sound manner. previously it was possible to do, but allowed users to start two concurrent transfers to the same fifo using different dma channels, which obviously would not have the expected results on average.

Co-authored-by: pennae <github@quasiparticle.net>

this *finally* allows sound implementions of bidirectional transfers

without blocking. the futures previously allowed only a single direction

to be active at any given time, and the dma transfers didn't take a

mutable reference and were thus unsound.

we can only have one active waiter for any given irq at any given time.

allowing waits for irqs on state machines bypasses this limitation and

causes lost events for all but the latest waiter for a given irq.

splitting this out also allows us to signal from state machines to other

parts of the application without monopolizing state machine access for

the irq wait, as would be necessary to make irq waiting sound.

move all methods into PioStateMachine instead. the huge trait wasn't

object-safe and thus didn't have any benefits whatsoever except for

making it *slightly* easier to write bounds for passing around state

machines. that would be much better solved with generics-less instances.

1425: rp pio, round 2 r=Dirbaio a=pennae

another round of bugfixes for pio, and some refactoring. in the end we'd like to make pio look like all the other modules and not expose traits that provide all the methods of a type, but put them onto the type itself. traits only make much sense, even if we added an AnyPio and merged the types for the member state machines (at the cost of at least a u8 per member of Pio).

Co-authored-by: pennae <github@quasiparticle.net>

not requiring a PioInstance for splitting lets us split from a

PeripheralRef or borrowed PIO as well, mirroring every other peripheral

in embassy_rp. pio pins still have to be constructed from owned pin

instances for now.

merge into PioInstance instead. PioPeripheral was mostly a wrapper

around PioInstance anyway, and the way the wrapping was done required

PioInstanceBase<N> types where PIO{N} could've been used instead.

add an hd44780 example for pio. hd44780 with busy polling is a pretty

complicated protocol if the busy polling is to be done by the

peripheral, and this example exercises many pio features that we don't

have good examples for yet.

1376: rtc: cleanup and consolidate r=Dirbaio a=xoviat

This removes an extra file that I left in, adds an example, and consolidates the files into one 'v2' file.

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

1414: rp: report errors from buffered and dma uart receives r=Dirbaio a=pennae

neither of these reported errors so far, which is not ideal. add error reporting to both of them that matches the blocking error reporting as closely as is feasible, even allowing partial receives from buffered uarts before errors are reported where they would have been by the blocking code. dma transfers don't do this, if an errors applies to any byte in a transfer the entire transfer is nuked (though we probably could report how many bytes have been transferred).

Co-authored-by: pennae <github@quasiparticle.net>

instruction memory is a shared resource. writing it only from PioCommon

clarifies this, and perhaps makes it more obvious that multiple state

machines can share the same instructions.

this also allows *freeing* of instruction memory to reprogram the

system, although this interface is not entirely safe yet. it's safe in

the sense rusts understands things, but state machines may misbehave if

their instruction memory is freed and rewritten while they are running.

fixing this is out of scope for now since it requires some larger

changes to how state machines are handled. the interface provided

currently is already unsafe in that it lets people execute instruction

memory that has never been written, so this isn't much of a drawback for now.

pin and irq operations affect the entire pio block. with pins this is

not very problematic since pins themselves are resources, but irqs are

not treated like that and can thus interfere across state machines. the

ability to wait for an irq on a state machine is kept to make

synchronization with user code easier, and since we can't inspect loaded

programs at build time we wouldn't gain much from disallowing waits from

state machines anyway.

- probe-run screwed up the last release 2 weeks ago and it's still not fixed (issue 391). Doesn't look well maintained.

- Even when it's not broken, it lags behind probe-rs-cli in new chips support because it's slow in updating probe-rs.

1379: enable inline-asm feature for cortex-m in examples r=Dirbaio a=pennae

inline assembly is supported since rust 1.59, we're way past that. enabling this makes the compiled code more compact, and on rp2040 even decreses memory usage by not needing thunks in sram.

Co-authored-by: pennae <github@quasiparticle.net>

inline assembly is supported since rust 1.59, we're way past that.

enabling this makes the compiled code more compact, and on rp2040

even decreses memory usage by not needing thunks in sram.

1369: Lora AFIT r=Dirbaio a=Dirbaio

Extracted out of #1367

Probably we should wait until `rust-lorawan` is merged+released?

Co-authored-by: Ulf Lilleengen <lulf@redhat.com>

1371: RTC r=Dirbaio a=xoviat

This adds RTC for most of the stm32 chips. Nearly all of the work was not done by me, but I took it the last bit by disabling the chips that weren't working. I think it would be easier to enable them in future PRs if requested.

1374: stm32: remove TIMX singleton when used on timer driver r=Dirbaio a=xoviat

After multiple ways of looking at this, this is the best solution I could think of.

Co-authored-by: Mathias <mk@blackbird.online>

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

1330: stm32/pwm: add complementary pwm r=Dirbaio a=xoviat

This implements complementary PWM with dead time on many supported targets. The specific dead-time programming functions are passed through directly to the user, which is a bit ugly but the best compromise I could reach for now.

Co-authored-by: xoviat <xoviat@users.noreply.github.com>

1333: STM32: Adc V1 r=Dirbaio a=GrantM11235

Based on #947

Co-authored-by: Matthew W. Samsonoff <matt.samsonoff@gmail.com>

Co-authored-by: Grant Miller <GrantM11235@gmail.com>

1321: executor: add Pender, rework Cargo features. r=Dirbaio a=Dirbaio

This introduces a `Pender` struct with enum cases for thread-mode, interrupt-mode and

custom callback executors. This avoids calls through function pointers when using only

the thread or interrupt executors. Faster, and friendlier to `cargo-call-stack`.

`embassy-executor` now has `arch-xxx` Cargo features to select the arch and to enable

the builtin executors (thread and interrupt).

Co-authored-by: Dario Nieuwenhuis <dirbaio@dirbaio.net>

1313: (embassy-stm32): rework bufferedUart to get rid of PeripheralMutex r=Dirbaio a=MathiasKoch

New implementation is very similar to the implementation of embassy-nrf & embassy-rp.

Also adds embedded-hal traits to bufferedUart.

**NB**: Still needs testing on actual hardware

Co-authored-by: Mathias <mk@blackbird.online>

This introduces a `Pender` struct with enum cases for thread-mode, interrupt-mode and

custom callback executors. This avoids calls through function pointers when using only

the thread or interrupt executors. Faster, and friendlier to `cargo-call-stack`.

`embassy-executor` now has `arch-xxx` Cargo features to select the arch and to enable

the builtin executors (thread and interrupt).

This example also uses a pio program compiled at runtime, rather than one built at compile time. There's no reason to do that, but it's probably useful to have an example that does this as well.

> dirbaio: so I was checking how zephyr does UARTE RX on nRF

> dirbaio: because currently we have the ugly "restart DMA on line idle to flush it" hack

> dirbaio: because according to the docs "For each byte received over the RXD line, an RXDRDY event will be generated. This event is likely to occur before the corresponding data has been transferred to Data RAM."

> dirbaio: so as I understood it, the only way to guarantee the data is actually transferred to RAM is to stop+restart DMA

> dirbaio: well, guess what?

> dirbaio: they just count RXDRDY's, and process that amount of data without restarting DMA

> dirbaio: with a timer configured as counter https://github.com/zephyrproject-rtos/zephyr/blob/main/drivers/serial/uart_nrfx_uarte.c#L650-L692

> dirbaio: 🤔🤷⁉️

> dirbaio: someone saying you can do the "hook up rxdrdy to a counter" trick, someone else saying it's wrong 🤪https://devzone.nordicsemi.com/f/nordic-q-a/28420/uarte-in-circular-mode

So we're going to do just that!

- BufferedUarte is lock-free now. No PeripheralMutex.

- The "restart DMA on line idle to flush it" hack is GONE. This means

- It'll work correctly without RTS/CTS now.

- It'll have better throughput when using RTS/CTS.

The UARTETWISPIn naming is quite horrible. With the nRF53, Nordic realized this

and renamed the interrupts to SERIALn. Let's copy that for our peripheral names, in nrf53 and nrf91.

They're used to communicate from the app to ST's OTA bootloader. See AN5247.

This bootloader is optional, must be flashed by the user, and requires changing the FLASH start address as well, so the current memory regions still require modifications to use it. Therefore there's no point in reserving these words.

Thanks @adamgreig for investigating the purpose.

1218: Lora: sx126x: Change timing window to match values found experimentally. r=Dirbaio a=CBJamo

As mentioned in #1188.

1219: stm32/sdmmc: Fix SDIOv1 writes r=Dirbaio a=chemicstry

This fixes writes on sdmmc v1 (SDIO). I'm pretty sure I tested writes in #669, but maybe I was just lucky or I just forgot.

There were two problems:

- Writes require DMA FIFO mode, otherwise SDIO FIFO is under/overrun depending on sdio/pclk2 clock ratio.

- Hardware flow control is broken for sdmmc v1 (I checked F1 and F4 erratas). This causes clock glitches above 12 MHz and results in write CRC errors.

Co-authored-by: Caleb Jamison <caleb@cbjamo.com>

Co-authored-by: chemicstry <chemicstry@gmail.com>

1217: Fix a typo in "PioPeripheral" r=Dirbaio a=SekoiaTree

Renames "PioPeripherial" to "PioPeripheral" (without the second i).

Co-authored-by: sekoia <sequoia.1009@gmail.com>

- Allows classes to handle vendor requests.

- Allows classes to use a single handler for multiple interfaces.

- Allows classes to access the other events (previously only `reset` was available).

This brings it inline with the other embassy-usb descriptor APIs and allows it to integrate well with the Builder to allow class constructors to add MS OS descriptors.

Also adds a `usb_serial_winusb` example to demonstrate how to use the API.

1173: nRF examples crates names r=lulf a=davidedellagiustina

Fixed nRF examples crates' names: they had the same names and they were conflicting during compilation (Cargo warning).

1174: add missing copy of icmpv6 checksum r=lulf a=lulf

add proto-ipv6 feature to stm32h7 example to catch issues in CI

Co-authored-by: Davide Della Giustina <davide@dellagiustina.com>

Co-authored-by: Ulf Lilleengen <lulf@redhat.com>

1142: More rp2040 BufferedUart fixes r=Dirbaio a=timokroeger

* Refactor init code

* Make it possible to drop RX without breaking TX (or vice versa)

* Correctly handle RX buffer full scenario

Co-authored-by: Timo Kröger <timokroeger93@gmail.com>

1147: Support codesigning in the firmware updater r=lulf a=huntc

This PR provides a method to verify that firmware has been SHA-512 hashed and signed with a private key given its public key. The implementation provides both [`ed25519-dalek`](https://github.com/dalek-cryptography/ed25519-dalek/blob/main/Cargo.toml) and [`salty`](https://github.com/ycrypto/salty) as the signature verifiers. Either of the `ed25519-dalek` and `ed25519-salty` features is required to enable the functionality from `embassy-boot`.

The `verify_and_mark_updated` method is used in place of `mark_updated` when signing is used via its feature. This avoids the accidental omission of validation where it has been declared as required at compile time. It also keeps the parity of calls at the same number to the previous situation.

The PR permits other types of signature verifiers in the future on the proviso that the [Signature trait](https://github.com/RustCrypto/traits/tree/master/signature) is supported.

Finally, I've updated the CI to include testing `embassy-boot`, which it was doing before. In addition, I've included a unit test for verification based on a `ed25519-dalek` documentation example. This tests both the `dalek` and `salty` implementations.

In terms of code size comparisons, `dalek` adds about 68KiB and `salty` adds about 20KiB. I'm using `salty` myself. I've also tested this out by signing my code with the OpenBSD `signify` utility and then verify it during firmware upload using `salty`.

Co-authored-by: huntc <huntchr@gmail.com>

This commit provides a method to verify that firmware has been signed with a private key given its public key. The implementation uses ed25519-dalek as the signature verifier. An "ed25519" feature is required to enable the functionality. When disabled (the default), calling the firmware updater's verify method will return a failure.

1141: feat: compile bootloader examples for nRF91 r=lulf a=lulf

* Add nRF91 as target in CI builds

* Add example linker scripts for nrf91

* Make less nRF52 assumptions example config

* Add llvm-tools-preview required for cargo objcopy example

Co-authored-by: Ulf Lilleengen <lulf@redhat.com>

* Add nRF91 as target in CI builds

* Add example linker scripts for nrf91

* Make less nRF52 assumptions example config

* Add llvm-tools-preview required for cargo objcopy example

1139: Wdt config changes r=lulf a=huntc

Per commits:

* By passing WDT config around we can control it more easily and promote sharing it between files.

* The memory layout of the s140 crept into a number of memory files, which can cause confusion (well, it did for me!).

* Obtaining the current WDT config is useful so that we do not have to duplicate configurations around the place. A constructor method has been introduced that attempts to return the current running WDT config from the WDT peripheral. The bootloader example has also been updated to show how the watchdog can be obtained and used.

Co-authored-by: huntc <huntchr@gmail.com>

Obtaining the current WDT config is important so that we do not have to duplication configuration around the place. A constructor method has been introduced that returns WDT config in accordance with how the register is presently configured. The bootloader example has also been updated to show the watchdog can be obtained and used.

1093: Add random example r=Dirbaio a=miathedev

Thanks Lulf for the help!

This should be added as example so other people can look it up easily.

With love,

Mia

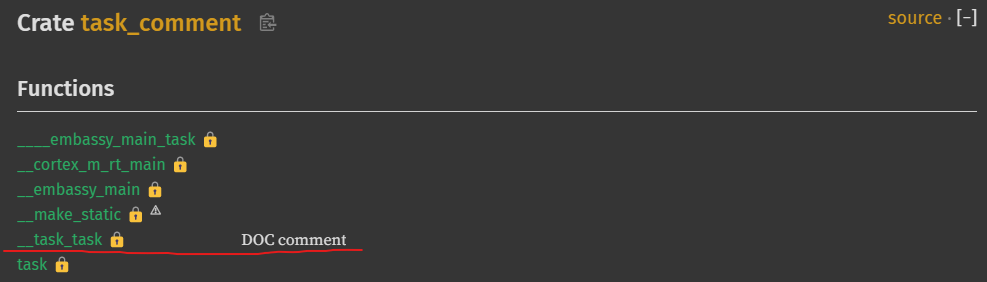

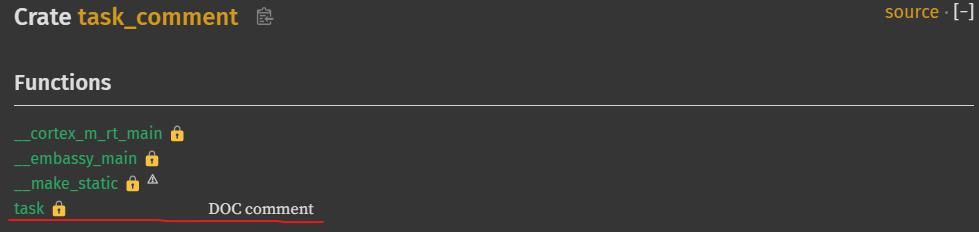

1127: clean up doc comment generation r=Dirbaio a=Weshnaw

I noticed that when I created doc comments for my tasks that the doc comments got included on the inner function but not the outer functions, I personally prefer keeping the documentation as clean as possible so this PR aims to hide the inner function and then add doc comments to the outer function.

The actual changes include:

* adding #[doc(hidden)] onto the `task_inner` function

* I flip flopped on this one because I could imagine someone may want this in their docs, but decided to include but I think arguments could be made either way

* copy the attributes from `task_inner` to `task_outer`

* I don't work with proc_macros often so I am not entirely sure if the way I went about it is correct but it seems to work fine

* specifically: using `parse_quote` to create the `task_outer` as a `ItemFn` then duplicating the attributes from `task_inner` to `task_outer`

* I also am not sure if it's a good idea to duplicate all attributes over, but I honestly wasn't sure how to just get the just doc comment attributes

Co-authored-by: miathedev <mia@metzler.systems>

Co-authored-by: Brendon Fallquist <bfallquist@gmail.com>

modify RP2040 adc example to get inside biased bipolar diode voltage,

then convert this temperature sensor data into Celsius degree,

according to chapter 4.9.5. Temperature Sensor in RP2040 datasheet.

The eth code is always built and available, but has no own API (other

than the embassy-net Device impl) to rx/tx packets. We could add this

API in the future, so the feature only means "embassy-net support".

1043: Rpi Pico PIO driver r=Dirbaio a=fluffware

This is a driver for the two PIOs in the Pico. I've tried using the type system to get as much compile time checks as possible. There is asynchronous support for FIFOs an Irqs. No DMA support yet. There's an example that shows how to use the driver asynchronously.

1103: embassy-stm32: add rs485 driver enable to uart r=Dirbaio a=FrozenDroid

Co-authored-by: Simon Berg <ksb@fluffware.se>

Co-authored-by: Vincent Stakenburg <v.stakenburg@sinewave.nl>

1089: feat: embassy-boot for rp2040 r=Dirbaio a=lulf

Add embassy-boot support for RP2040, with examples for the Raspberry Pi Pico.

Co-authored-by: Ulf Lilleengen <lulf@redhat.com>

1074: Added blinky example for stm32f0 r=lulf a=imrank03

Hi, I have added **blinky** example for `stm32f0` and tested with Nucleo board `STM32F091RC`.

- Can I add more example for stm32f0?

Co-authored-by: @imrank03 <immu0396@gmail.com>

1056: embassy-nrf: Add TWIS module r=Dirbaio a=kalkyl

Verified to be working on nrf9160

Co-authored-by: kalkyl <henrik.alser@me.com>

Co-authored-by: Henrik Alsér <henrik.alser@me.com>

1042: embassy-nrf: Add SPIS module r=Dirbaio a=kalkyl

Verified to be working on nrf9160

Co-authored-by: Henrik Alsér <henrik.alser@me.com>

Co-authored-by: Henrik Alsér <henrik.alser@ucsmindbite.se>

Co-authored-by: kalkyl <henrik.alser@me.com>

1024: stm32/adc: Remove voltage and temperature conversions r=Dirbaio a=GrantM11235

The current conversion utilities are confusing and a bit of a footgun. (Two out of the three examples got it wrong! They didn't measure vref at all, so all the conversions are completely wrong if vcca isn't 3.3v)

I think we should eventually have some sort of conversion utilities in the HAL, but for now I think it is best to just remove it and let the users do their own math.

cc `@chemicstry`

Co-authored-by: Grant Miller <GrantM11235@gmail.com>

1025: Implement I2C timeouts, second attempt r=Dirbaio a=chemicstry

This is an alterrnative to #1022 as discussed there.

Timeouts are implemented using suggested `check_timeout: impl Fn() -> Result<(), Error>` function, which does not depend on `embassy-time` by default and is a noop for regular I2C.

This also adds `time` feature like in `embassy-nrf` to enable `embassy-time` dependencies. While at it, I also gated some other peripherals that depend on `embassy-time`, notably `usb` and (partially) `subghz`.

`TimeoutI2c` is currently only implemented for i2cv1, because i2cv2 has additional complications:

- Async methods still use a lot of busy waiting code in between DMA transfers, so simple `with_timeout()` will not work and it will have to use both types of timeouts. It could probably be rewritten to replace busy waits with IRQs, but that's outside the scope of this PR.

- I2C definition `I2c<'d, T, TXDMA, RXDMA>` is different from i2cv1 `I2c<'d, T>` making it hard to share single `TimeoutI2c` wrapper. A couple of options here:

- Duplicate `TimeoutI2c` code

- Add dummy `TXDMA`, `RXDMA` types to i2cv1 considering that in the future it should also support DMA

Co-authored-by: chemicstry <chemicstry@gmail.com>